ПОДРОБНАЯ ИНФОРМАЦИЯ

Заявку на получение дополнительной информации по этому проекту можно заполнить здесь.

|

Номер 84-090-00 |

|

Наименование проекта Запоминающее устройство с обнаружением ошибок и коррекцией одиночной ошибки |

|

Назначение Используется при разработке интегральных микросхем памяти, вычислительных машин и устройств |

|

Рекомендуемая область применения Вычислительная техника |

|

Описание

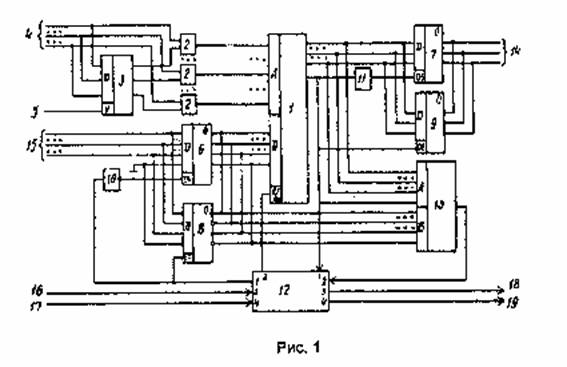

Запоминающее устройство с обнаружением ошибок и коррекцией одиночной ошибки содержит накопитель 1, сумматоры по модулю два 2, выходы которых соединены с адресными входами накопителя 1, регистр 3, выходы которого соединены с первыми входами сумматоров по модулю два 2, вторые входы которых соединены с информационными входами регистра 3 и являются адресными входами 4 устройства. Кроме того, в него введены первый 6 и второй 7 шинные формирователи, первый 8 и второй 9 инвертирующие шинные формирователи, первый 10 и второй 11 элементы НЕ, формирователь управляющих сигналов 12 и блок сравнения 13, входы первой группы которого, кроме последнего, информационные входы второго шинного формирователя 7 и второго инвертирующего шинного формирователя 9 соответственно объединены и подключены к выходам накопителя 1, информационные входы которого и входы второй группы блока сравнения 13 соответственно объединены и подключены к соответственно объединенным выходам первого шинного формирователя 6 и первого инвертирующего шинного, формирователя 8, информационные входы которых, кроме последнего, соответственно объединены и являются информационными входами 15 устройства, последние информационные входы первого шинного формирователя 6 и первого инвертирующего шинного формирователя 8 объединены и подключены к шине нулевого потенциала устройства, управляющие входы первого инвертирующего шинного формирователя 8 и через первый элемент НЕ 10 первого шинного формирователя 6 объединены и подключены к первому выходу формирователя управляющих сигналов 12, первый вход которого, последний вход первой группы блока сравнения 13, управляющий вход второго инвертирующего шинного формирователя 9 и. через второй элемент НЕ 11, управляющий вход второго шинного формирователя 7 объединены и подключены к выходу дополнительного разряда накопителя 1. управляющий вход накопителя 1 соединен со вторым выходом формирователя управляющих сигналов 12, второй вход которого соединен с выходом блока сравнения 13, выходы второго шинного формирователя 7 и второго инвертирующего шинного формирователя 9 соответственно объединены и являются информационными выходами 14 устройства, входом задания режима 5 которого является управляющий вход регистра 3, третий и четвертый входы и третий и четвертый выходы формирователя управляющих сигналов являются соответственно входами записи 16 и чтения 17 и выходами сигнала готовности 18 и ошибки 19 устройства.

|

|

Преимущества перед известными аналогами Аналоги не известны |

|

Стадия освоения Внедрено в производство |

|

Результаты испытаний Технология обеспечивает получение стабильных результатов |

|

Технико-экономический эффект Повышение надежности вычислительного оборудования |

|

Возможность передачи за рубеж За рубеж не передаётся |

|

Дата поступления материала 27.07.2000 |

Инновации и люди

У павильонов Уральской выставки «ИННОВАЦИИ 2010» (г. Екатеринбург, 2010 г.)

Мероприятия на выставке "Инновации и инвестиции - 2008" (Югра, 2008 г.)

Открытие выставки "Малый бизнес. Инновации. Инвестиции" (г. Магнитогорск, 2007 г.)

Демонстрация разработок на выставке "Малый бизнес. Инновации. Инвестиции" (г. Магнитогорск, 2007 г.)